如果TXC晶振在应用在电路主板后功能不正常或根本无法工作,请使用下面的清单确定可能的问题,请按照说明确定因素和可能的解决方案。

01:晶体无信号输出

02:系统无法正常工作,因为晶体没有足够的输出波形幅度。

03:由于频率输出的偏差超出极限,系统无法运行。

04:频率输出仅为目标频率的三分之一。

05:频率输出是目标频率的三倍。

06:由于输出波形幅度过大导致系统故障。

07:由于输出波形而导致的系统故障或图像在监视器上显示时被其他信号中断。

08:电路的EMI高。

09:将晶体安装在PCB上时不会振动。

10:在PCB上进行热测试时,晶体无法工作或频率偏移。

11:晶体的频率可拉性不足或频率不对称变化。

12:当将晶体安装在PCB上时,频率随时间的分布范围过大,或者频率受杂散电容的影响很大。

01:晶体无信号输出

1-1。

请使用示波器或频率计数器测量晶体的两个端子输出的信号。如果没有信号输出,请按照步骤1-1至步骤1-4执行检查。如果晶体的外部端子(Xout)有信号输出,而晶体内部的端子(Xin)无信号输出,请按照步骤1-5至步骤1-6检查晶体。

1-2。

请卸载晶体,并测试其频率和负载电容,以使用专业的测试机查看它们是否振动并符合您的规格。您也可以将其发送给您的供应商,让他们为您测试。

1-3。

如果出现以下任何一种情况,晶体不振动,其负载电容不符合您的规格,或者电流频率与目标频率之间存在巨大差距,请将该晶振发送给您的供应商进行质量分析。如果频率和负载电容符合您的规格,我们将需要进行等效电路测试。

1-4。

等效电路测试

1-4-1。

通常,微处理器的振荡电路来自如下的Colpitts电路:

图1

Cd和Cg是外部负载电容,已内置在芯片组中。(请参阅芯片组的规格)

Rf是200KΩ?1MΩ的反馈电阻。它通常内置在芯片组中。

Rd是具有470Ω?1KΩ的极限电阻。该电阻对于普通电路不是必需的,而仅对于具有高电源的电路是必需的。

1-4-2。

稳定的振荡电路需要负电阻,并且其值至少应为晶体电阻的五倍。可以写成|-R|>5Rr。

例如,要获得稳定的振荡电路,当晶体电阻值为40Ω时,IC的负电阻值必须小于200Ω。

1-4-3。

“负阻力” 是评估振荡电路质量的准绳。在某些情况下,例如老化,热变化,电压变化等,如果“ Q”的值,电路可能不会振荡。低。因此,按照以下说明测量负电阻(-R)非常重要:

(1)将电阻(R)与晶体串联连接

(2)从起始点到电阻调整R的值振荡的停止点。

(3)在振荡期间测量R的值。

(4)您将可以获得负电阻值|| R ||。= R+Rr,Rr=晶体电阻。

PS连接电路的杂散电容可能会影响测量值。

1-4-4。

如果晶体的参数正常,但在振荡电路中无法稳定工作,则我们必须找出IC的电阻值是否太低而无法驱动电路。如果是这样,我们可以通过三种方法来改善这种情况:

降低外部电容(Cd和Cg)的值,并采用具有较低负载电容(CL)的其他晶体。

采用低电阻(Rr)的晶体。

使用Cd和Cg值不相等的设计。我们可以增加Cd(Xout)的负载电容,并减小Cg(Xin)的负载电容,以提高来自Xin的波形幅度输出,该输出将在其后端电路中使用。

1-5。

当从Xout输出信号但没有从Xin输出信号时,则表示后电极后端电路的功耗非常大。我们可以在电路的输出与其后电极之间添加一个缓冲器,以驱动后端电路。

1-6。

除了上述1-5的方法外,您还可以按照步骤1-4-4中的三种方法进行操作。如果您的问题无法解决,请联系晶振或IC制造商的现场应用工程师寻求进一步的帮助。

02:系统无法正常工作,因为晶体没有足够的输出波形幅度。

2-1。

请使用示波器或频率计数器测量来自晶体两个端子的信号,如果频率不在规格范围内,并且其输出波形幅度不足(例如,超过+/- 200ppm),请执行以下步骤2-3至步骤2-5。

2-2。

电容与频率的公式如下:

| FL = FR *(1 + C1 / 2 *(C0 + CL))其中 |

该曲线表示电容变化随频率变化的变化(频率可拉性):

如果频率计数器测量的频率高于目标频率,则应增加电容值(CL或Cd和Cg)以降低频率转换为目标频率,反之亦然。

调整频率后,请检查波形幅度是否有所改善。如果得到改善,则说明电路的原始设计没有调整到晶体的最佳谐振点。调整谐振点后,晶体应能正常工作。

2-3。

如果即使频率非常接近目标频率也没有改善波形幅度,则可以使用以下三种方法来改善它:

方法1:降低外部电容(Cd和Cg)的值,并采用具有较低负载电容(CL)的晶体。

方法2:采用低电阻(Rr)的晶体。

方法3:使用Cd和Cg值不相等的设计。

我们可以增加Cd(Xout)的负载电容,并减小Cg(Xin)的负载电容,以提高将在其后端电路中使用的Xin的波形幅度输出。

我们建议您使用上述方法来节省成本并确保安全。

2-4。

请使用频率计数器测量晶体,以确保在提高波形幅度后,调整后的频率仍符合原始规格。如果频率不符合规格,请根据您的目标频率选择具有合适CL值的晶体。

2-5。

如果频率远高于目标频率,请选择CL较低的晶体,反之亦然。

03:由于输出频率的高偏差,系统无法运行。

3-1。

通过以下方法可以解决频率输出偏差超过极限的问题:

调整外部电容Cd和Cg的值。

如果通过频率计数器测量的频率高于目标频率,则应增加外部电容CL(或Cd和Cg的值),以将频率降低至目标频率,反之亦然。

采用具有不同电容值(CL)的晶体。

如果频率远高于目标频率,则采用电容较低的晶体,反之亦然。

3-2。

使用正确的电容并将频率调整为目标值后,请使用示波器检查波形幅度是否正常。如果由于增加了外部电容而导致波形幅度减小,请使用方法2来调整频率(较低的外部电容并采用较低电容的晶体)。

04:频率输出仅为目标频率的三分之一.

4-1。

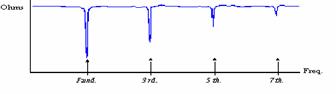

下面的曲线代表了晶体电阻的特性:

晶体具有各种振动模式,例如基本振动,第三泛音,第五泛音等。当应用基本模式时,晶振的电阻为最低,这意味着晶体最容易振荡。当应用第三音频模式时,必须利用放大电路将基本模式的频率反馈降低到小于第三音频模式的程度。因此,如果频率仅为目标频率的三分之一,则由于电路环境适合于基本模式而不是第三音调模式,因此应检查是否应用了放大电路或其设置值是否合适。

4-2。

如果未应用放大电路或其设置值不足够,电路可能不会振荡。

4-3。

基本模式和第三音调模式的应用如下:

| 一个。基本模式的应用 | b。第三音调模式的应用 |

|

|

4-4。

下表显示了不同频率下第三音模式的L,C匹配值:

| 第三泛音频率 | 大号 | C |

| 25 Mhz?35 Mhz | 22小时 | 220 pF |

| 35 Mhz?45 Mhz | 5.5小时 | 690 pF |

| 45 Mhz?60 Mhz | 1小时 | 1500 pF |

| 60兆赫?80兆赫 | 550牛顿 | 2200 pF |

| 80兆赫?100兆赫 | 220牛顿 | 4700 pF |

05:频率输出是目标频率的三倍

5-1。

此问题的机会相对较小。请确定由于放大电路,第三音调模式的频率反馈是否大于基本模式的反馈。当放大电路内置在芯片组中时,可能会发生此问题。要解决此问题,请采用三音模式晶体。

5-2。

此外,不适用于第三音调模式的放大电路设计也可能导致电路以第五音调模式振荡或无法振荡。

06:由于输出波形幅度过大导致系统故障。

6-1。

请参考情况2的解决方法。请增加端子Xin的电容,然后检查波形幅度是否有所改善。

07:由于输出波形而导致的系统故障或图像在监视器上显示时被其他信号中断。

7-1。

请使用Spectrum Analyzer机器确定中断信号的频率。我们可以根据频率找出问题所在。

7-2。

如果它是来自电源的交流信号,请检查电源和信号两地的状态是否浮空。如果不是,请更改为浮动。

7-3。

如果信号具有高频,请使用以下方法:

以水晶壳为接地。

采用C0较小的晶体。

增加电路的外部电容Cd和Cg,并采用具有更高负载电容CL的晶体。

7-4。

如果上述方法不能解决您的问题,请检查周围电路和PCB布局。如果它们都正常,请要求IC制造商调查其芯片组设计对未知信号的反应。改变周围电路的设计只能缓解问题,而不能完全解决问题。通常。最好找出并解决芯片组设计问题。

08:电路的EMI过大

8-1。

该问题的解决方案与问题7相同。请参考步骤7-1至步骤7-4。

09:将晶体安装在PCB上时不会振荡。

9-1。

请使用示波器或频率计数器测量来自晶体两个端子的信号。请按照步骤9-1至9-4进行测试。当Xin有信号输出但其波形幅度较小时,请按照步骤2-1-2-5进行测试。

9-2。

请卸载晶体,并测试其频率和负载电容,以使用专业的测试机查看它们是否振动并符合您的规格。您也可以将其发送给您的供应商,让他们为您测试。

9-3。

如果发生以下任何一种情况,例如,晶体不振动,其负载电容不符合您的规格,或者电流频率与目标频率之间存在巨大差距,请将晶体发送至供应商进行质量分析。

9-4。

如果频率和负载电容符合您的规格,并且晶体通过了DLD测试,则我们需要进行等效电路测试。请参考步骤1-4-1-6。

9-5。

如果晶体未通过DLD测试,请发送给您的供应商进行质量分析以进一步改进。

10:在PCB上进行热测试时,晶体不会振动或频率漂移。

10-1。

卸载晶体,并使用热测试机测试其频率和电阻,以查看其是否振荡并符合规格。您也可以将其发送给晶体供应商进行测试。(热测试点的间隔至少应为10°/ 1测试点)

10-2。

如果在工作温度范围内其电阻和频率超出规格,请将晶振发送给制造商进行质量分析和进一步改进。

10-3。

如果晶体通过热测试,请检查振荡电路和其他元件的特性,例如其外部电容的温度特性,芯片电路的温度特性等。

11:晶体的频率可拉性不足或频率不对称变化。

11-1。

如下所示,VCXO电路的电容与可拉性之间存在负相关关系,这意味着,当电容减小时,频率牵引范围(FL-Fr)会增大,反之亦然。/由于VCXO电路的电容是由压敏电阻控制的,因此我们可以通过使用电容较小或调节范围较大的压敏电阻来扩大拉频范围。

11-2。

除外部电路调整外,晶振参数的特性也会影响频率牵引范围。其参考参数是微调灵敏度(TS),C0/C1(r),C1,C0等。每个参数与频率可拉性之间的关系如下:

C0→C1,C1→C0/C1(r),TS,可拉性

11-3。

如果拉频范围不足,我们也可以调整晶体的规格以达到目标范围。

11-4。

当一侧的拉力不够大而另一侧由于拉力范围不对称而太大时,我们可以调整晶体的负载电容(CL)以达到对称性,并且两边都足够拉力。

12:如果晶体应用在PCB上,容易获得频率的扩展分布,并且频率受杂散电容的影响很大。

12-1。

根据11-1所示的晶体拉力曲线,电容越小,对频率变化的影响越大。如果频率分布太宽,请遵循以下方法:

a。)增加电容Cd和Cg的值,并采用具有较大负载电容(CL)的晶体。

b。)对Cd和Cg使用更复杂的电容(电容变化很小)。

c。)使用更精密的晶体(频率变化很小)。

方法(a)和方法(b)是有效的,并且可以节省更多成本。

12-2。

此外,如果由于PCB的杂散电容相对较大而无法改善频率分布以满足规格要求,则可能需要基于杂散电容源的新布局。